Intel donne une nouvelle impulsion à sa gamme de processeurs Itanium. Rappelons d’emblée que, dans la plupart des cas, les serveurs qui en sont équipés nt vocation à supporter des applications critiques. Les Itanium Poulson viendront remplacer les actuels Tukwila (Itanium 9300) en 2012. Le processeur (CPU) gravé en 32nm d’Intel sera enrichi de nouvelles fonctionnalités présentes sur le silicium et de nouvelles instructions.

Cette nouvelle gamme a été présentée à l’ISSCC (conférence des concepteurs de circuits intégrés) qui s’est tenue fin février à San Francisco. Mais elle s’est retrouvée de nouveau sur le devant de la scène lors de la conférence Hot Chips (17-19 août, Standford).

Au coeur des serveurs Unix de HP sur base IA-64 (Intel Architecture 64 bits), on trouve les CPU Itanium 9300 Tukwila qui sont gravés en 65 nm. Ils trouveront donc leur successeur dès 2012 avec les Poulson gravés en 32 nm.

Intel fait ainsi l’impasse sur une génération d’Itanium gravés en 45 nm puisque les Poulson devaient initialement arriver sur le marché en 2009 dans cette technologie. Trois années de retard qui auront permis à Intel d’effectuer des mises à jour architecturales substantielles.

Itanium Poulson : deux fois plus d’instructions exécutées par cycle

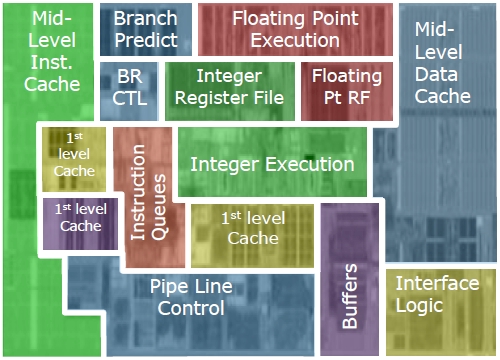

Le Poulson conservera les caractéristiques générales annoncées. A savoir huit coeurs (4 pour le Tukwila) et la possibilité de 16 threads ou coeurs virtuels contre 8 pour son prédécesseur. C’est la voie ouverte à l’exécution de deux fois plus d’instructions par cycle (12 contre 6 pour le Tukwila). Il disposera bien des 54 Mo de cache et un bus QPI (et SMI) à 6,4 GT/s (ou Giga Transfert par seconde) sera assuré. Par comparaison, on était à 4,8 GT/s pour le Tukwila.

Les fonctionnalités RAS (acronyme de « Reliability, Availability and Serviceability ») sont enrichies avec la technologie IRT (Instruction Replay Technology).*

Les erreurs sont de facto limitées grâce à l’intégration de caches sur le pipeline entre les différents étages. Il s’agit d’autant de mémoires qui permettront d’exécuter à nouveau une instruction depuis le buffer d’instruction en cas d’erreur.

C’est la promesse d’une résilience accrue limitant les crashs systèmes et la corruption de données. Et c’est un atout majeur s’agissant de microprocesseurs destinés à des serveurs haute disponibilité qui embarquent des CPU à architecture IA64.

L’Hyper-Threading est également amélioré grâce au Dual-Domain Multi-Threading. Des instructions indépendantes peuvent être simultanément présentes sur un même pipeline. Cela augmente le MIPS (Million d’instructions par seconde) du Poulson.

Le Poulson est aussi synonyme de nouvelles instructions présentes dans quatre unités de traitement du CPU. Au rang desquelles, on trouve des instructions relatives aux opérations sur les entiers, des instructions relatives au contrôle des threads…

Si le Poulson montre bien qu’Itanium n’est pas mort (n’en déplaise à Oracle), il est l’avant-garde du Kitson déjà en cours de développement. Les Poulson pourront remplacer les Tukwila puisqu’ils disposent d’une compatibilité dite « pin to pin » et se logeront donc dans le même socket.